智多晶SerDes 2.0 IP介绍

01智多晶SerDes IP已经升级到2.0版本

为了满足用户对SerDes日益增涨和多样化的要求。智多晶SerDes IP推出了2.0版本的升级,本次升级相比1.0版本主要带来了以下的变化:

增加了对SerDes内部的不同通道单独进行速率配置的功能

增加了同一路通道内部的TX和RX进行独立参数的配置的功能

增加了对每个单独通道的时钟来源(QPLL/CPLL)选择的功能

增加了从其他quad来的参考时钟来源的选择(North/South Route)功能

增加了选择输出时钟路径:PMA内部时钟或直接输出参考时钟

增加了RX/TX方向64B/66B 相关的功能

增加了Bypass SerDes内部FIFO的功能(使用延迟线代替)

增加了Channel Bonding(多通道绑定同步传输)的功能

02智多晶Serdes IP 2.0界面介绍

图1 SerDes IP 多通道单独页面配置

智多晶SerDes IP采用了灵活的配置界面可以对每个SerDes通道(channel)进行灵活的配置。如图1所示,用户可以定制对每个channel的速率,参考时钟频率,CPLL/QPLL的选择进行独立的配置,用以满足各种自定义项目中的需求。

图2 编码选择和时钟输出选择

目前SerDes 2.0已经支持了对8B/10B编码和64B/66B编码(Gearbox层以下)的配置选项。用户可以使用智多晶SerDes硬核的编码器完成8B/10B和64B/66B(Gearbox层以下)的对应功能 。IP界面也提供了对外部位宽和内部位宽的定制化配置。用户可以根据自己的系统和对应的上层协议来灵活的选取数据位宽。

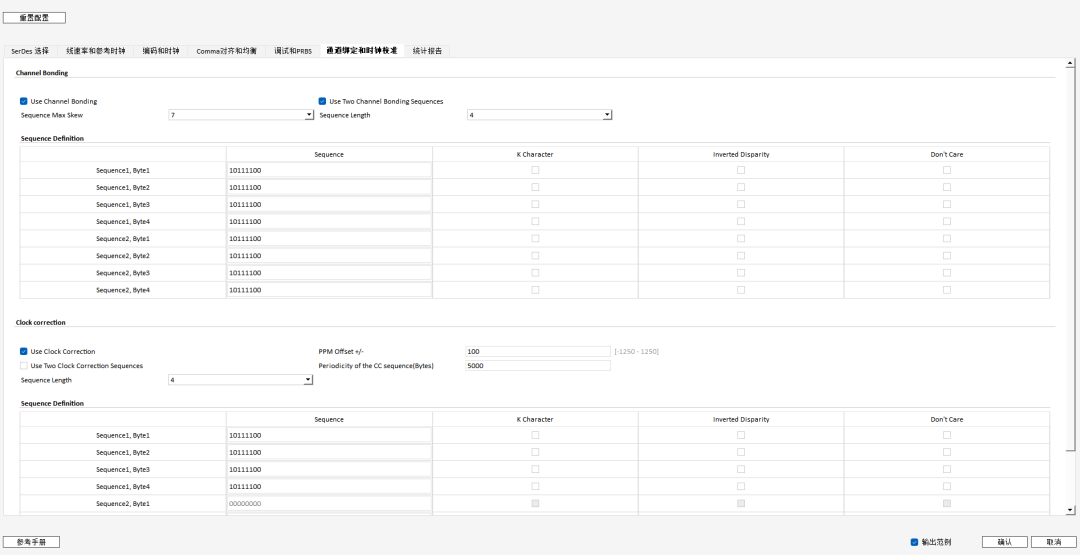

图3 通道绑定和时钟校准功能

目前SerDes 2.0已经支持了对通道绑定和时钟校准的功能。用户可以通过界面上的提示来完成相对应的配置。以通道绑定为例,可以设置具体的通道绑定所需要的码形长度和具体数值等。

图4 统计报告列表

在配置完成之后,SerDes 2.0 IP会生成对应的统计报告列表,用户可以通过浏览生成的统计报告列表来验证自己的IP是否满足自己的配置要求。同时提供了输出范例工程,供用户作为参考使用。

03智多晶SerDes IP 2.0的常用场景

SerDes(Serializer/Deserializer)是一种高速串行通信技术,主要用于将多路低速并行信号转换为高速串行信号,并通过传输媒体(如光缆或铜线)传输,然后在接收端再将串行信号转换回并行信号随着高速集成电路的发展,对高带宽,低延迟的协议需求越来越大。目前多种高速协议都可以以Serdes 为基础进行进一步的开发,用以完成高速通讯的目的。

目前常见的使用主要包括:

万兆以太网

CPRI

JESD204B

QSGMII

SRIO

XAUI

PCIE

AURORA

HDMI

DP/eDP

VByOne

目前智多晶Seal 5000系列产品SerDes的性能处于业界领先水平,SDM最大支持0.5-10.3125Gbps线速率,SDP最大支持0.5-6.6Gbps的线速率。SerDes最大速率受到PCB信号完整性设计,外界干扰等多种条件影响。如果要达到理论性能需要有相关设计保障,详细信息请咨询智多晶FAE。

- 东阳光拿到金额最高190亿算力大单 东莞首富抢占AI产业风口

- 五家上市险企一季度新业务价值普涨 是否已进入新一轮修复周期?

- 社保基金一季度持仓大盘点!重仓50强名单出炉 多只龙头被长期持有超10年

- 大反弹!A股悄然收复4100点 这波行情究竟在“涨”什么?

- 游族网络财报:海外收入占比创新高,AI赋能驱动盈利能力全面提升

- 兴业聚鑫灵活配置混合A:2026年第一季度利润205.23万元 净值增长率1.19%

- 4月29日北向资金最新动向(附十大成交股)

- 【风口研报】龙头业绩超预期加重要大会催化 创新药板块景气度有望持续上行

- 华为昇腾产业链爆发!最全名单来了

- 广发策略:公募基金加仓思路 围绕景气预期改善方向集中配置

- 牛散“鑫多多”现身“妖股”?持股超7亿元 公司连年亏损

- 财报观察室丨口子窖净利润创10年新低,高端酒持续萎缩

- 中办、国办印发《碳达峰碳中和综合评价考核办法》

- 中际旭创市值首破万亿,一年涨超10倍,公募基金头号重仓股

- 午后突变!致尚科技垂直20%涨停!A50直线拉升!

- 建信信息产业股票A:2026年第一季度利润2287.37万元 净值增长率5.22%